- 您现在的位置:买卖IC网 > Sheet目录368 > W631GG6KB-15 (Winbond Electronics)IC DDR3 SDRAM 1GBIT 96WBGA

�� �

�

�

�W631GG6KB�

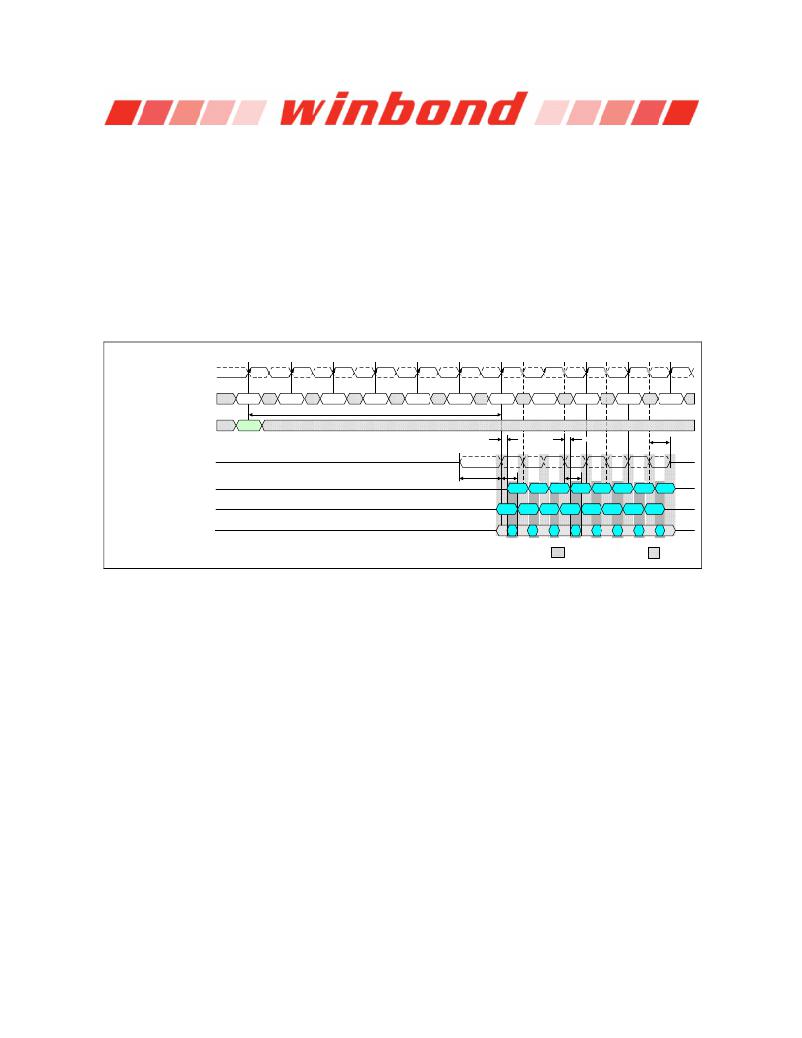

�8.13.2.2� READ� Timing;� Data� Strobe� to� Data� relationship�

�The� Data� Strobe� to� Data� relationship� is� shown� in� Figure� 25� and� is� applied� when� the� DLL� is� enabled�

�and� locked.�

�Rising� data� strobe� edge� parameters:�

�?�

�?�

�t� DQSQ� describes� the� latest� valid� transition� of� the� associated� DQ� pins.�

�t� QH� describes� the� earliest� invalid� transition� of� the� associated� DQ� pins.�

�Falling� data� strobe� edge� parameters:�

�?�

�?�

�t� DQSQ� describes� the� latest� valid� transition� of� the� associated� DQ� pins.�

�t� QH� describes� the� earliest� invalid� transition� of� the� associated� DQ� pins.�

�t� DQSQ� ;� both� rising/falling� edges� of� DQS,� no� t� AC� defined.�

�T0�

�T1�

�T2�

�T3�

�T4�

�T5�

�T6�

�T7�

�T8�

�T9�

�T10�

�CK#�

�CK�

�Command*� 3�

�READ�

�NOP�

�NOP�

�NOP�

�NOP�

�NOP�

�NOP�

�NOP�

�NOP�

�NOP�

�NOP�

�RL� =� AL� +� CL�

�Address*� 4�

�Bank�

�Col� n�

�DQS,� DQS#�

�t� DQSQ� (max)�

�t� DQSQ� (max)�

�t� RPST�

�t� RPRE�

�t� QH�

�t� QH�

�DQ*� 2� (Last� data� valid)�

�DQ*� 2� (first� data� no� longer� valid)�

�All� DQs� collectively�

�Dout�

�n�

�Dout�

�n�

�Dout�

�n�

�Dout�

�n+1�

�Dout�

�n+1�

�Dout�

�n+1�

�Dout�

�n+2�

�Dout�

�n+2�

�Dout�

�n+2�

�Dout�

�n+3�

�Dout�

�n+3�

�Dout�

�n+3�

�Dout�

�n+4�

�Dout�

�n+4�

�Dout�

�n+4�

�Dout�

�n+5�

�Dout�

�n+5�

�Dout�

�n+5�

�Dout�

�n+6�

�Dout�

�n+6�

�Dout�

�n+6�

�Dout�

�n+7�

�Dout�

�n+7�

�Dout�

�n+7�

�TRANSITIONING� DATA�

�DON'T� CARE�

�Notes:�

�1.� BL� =� 8,� RL� =� 6� (AL� =� 0,� CL� =� 6).�

�2.� Dout� n� =� data-out� from� column� n.�

�3.� NOP� commands� are� shown� for� ease� of� illustration;� other� commands� may� be� valid� at� these� times.�

�4.� BL8� setting� activated� by� either� MR0� A[1:0]� =� 00� or� MR0� A[1:0]� =� 01� and� A12� =� 1� during� READ� command� at� T0.�

�5.� Output� timings� are� referenced� to� V� DDQ� /2,� and� DLL� on� for� locking.�

�6.� t� DQSQ� defines� the� skew� between� DQS,� DQS#� to� Data� and� does� not� define� DQS,� DQS#� to� Clock.�

�7.� Early� Data� transitions� may� not� always� happen� at� the� same� DQ.� Data� transitions� of� a� DQ� can� vary� (either� early� or� late)� within�

�a� burst.�

�Figure� 25� –� Data� Strobe� to� Data� Relationship�

�Publication� Release� Date:� Dec.� 09,� 2013�

�Revision� A05�

�-� 46� -�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

W9412G6IH-5

IC DDR-400 SDRAM 128MB 66TSSOPII

W9412G6JH-5I

IC DDR SDRAM 128MBIT 66TSOPII

W9425G6EH-5

IC DDR-400 SDRAM 256MB 66TSSOPII

W9425G6JH-5I

IC DDR SDRAM 256MBIT 66TSOPII

W947D2HBJX5E

IC LPDDR SDRAM 128MBIT 90VFBGA

W948D2FBJX5E

IC LPDDR SDRAM 256MBIT 90VFBGA

W949D2CBJX5E

IC LPDDR SDRAM 512MBIT 90VFBGA

W971GG6JB25I

IC DDR2 SDRAM 1GBIT 84WBGA

相关代理商/技术参数

W631GG8KB-11

制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 1GBIT 制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 1GBIT 78WBGA

W631GG8KB-12

制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR3 SDRAM 1G-Bit 128Mx8 1.5V 制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 1GBIT 制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 1GBIT 78WBGA

W631GG8KB-15

制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 1GBIT 制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 1GBIT 78WBGA

W632

制造商:LUMINIS 制造商全称:LUMINIS 功能描述:Wall mount

W632GG6KB-11

制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 2GBIT 96WBGA

W632GG8KB-11

制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 2GBIT 78WBGA

W634

制造商:LUMINIS 制造商全称:LUMINIS 功能描述:Wall mount

W638

制造商:LUMINIS 制造商全称:LUMINIS 功能描述:Wall mount